Controlled Impedance PCB Design Guide: Stackup, Trace Geometry, and Manufacturing Handoff

SUNTOP Electronics

A fast digital or RF board can pass layout review and still fail the handoff to manufacturing. That is why controlled impedance PCB design needs to be treated as a release discipline, not just as a routing calculation.

In real projects, controlled impedance PCB design is the process of matching trace geometry, reference planes, dielectric spacing, copper assumptions, and fabrication communication so the board that gets built still behaves like the board that was designed. If any of those pieces are vague, the quote slows down, the stackup changes late, or the finished board no longer matches the intended signal environment.

This guide explains impedance-controlled board planning in a practical way. It focuses on when impedance control matters, how stackup and routing decisions need to move together, what a PCB supplier must know before quoting, and which mistakes most often create avoidable redesign loops.

What Controlled Impedance PCB Design Means and When It Matters

At a signal level, controlled impedance PCB design means designing interconnect structures so target impedance is intentional and repeatable instead of accidental. The theory sits on concepts such as characteristic impedance, but manufacturing success depends on how that theory is translated into a real stackup and fabrication package.

Not every board needs the same level of control. The requirement becomes more important when the design includes:

- RF paths or antennas

- high-speed serial channels

- DDR or other timing-sensitive buses

- longer traces where loss and reflection matter more

- mixed-signal layouts where noisy and sensitive nets share space

In those cases, impedance control is not only about hitting a target number like 50 ohms or 100 ohms differential. It is about protecting enough process margin that the supplier can actually build the intended structure without guessing what matters most.

How to Choose Stackup and Trace Geometry Together

The most common planning mistake in this kind of design work is treating stackup and routing as separate decisions. They are one system. Change dielectric thickness, copper thickness, prepreg behavior, or reference plane placement, and the trace geometry required for the same impedance target changes with it.

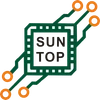

This fallback explainer illustration pairs routed traces with simplified layer structure to show why impedance control depends on stackup and geometry together.

That is why early stackup review matters. Before release, teams should check whether the proposed layer build, reference plane arrangement, and routing space are still compatible with realistic trace widths and spacing. The PCB Stackup Planner is useful for early package planning, and the Online Impedance Calculator helps teams sanity-check whether the geometry they want is even plausible before supplier review.

Microstrip and stripline decisions change manufacturability

A microstrip structure can be easier to route and inspect, but it is more exposed to surface conditions and local environment changes. A stripline is better shielded, yet it depends more heavily on internal layer control and stackup consistency. Good impedance-controlled routing strategy means choosing the structure that matches both signal behavior and manufacturing realism.

Material and copper assumptions must stay explicit

Even when the target impedance is fixed, the fabrication result depends on what material family, copper foil condition, and tolerance model the supplier uses. If the design assumes one dielectric profile and the quote is based on another, the release intent has already drifted before production starts.

What Manufacturing Data a PCB Supplier Needs to Quote It Correctly

A supplier cannot quote an impedance-controlled stackup accurately from Gerbers alone. The release package should make the design intent readable enough that the fabricator can review risk without reverse-engineering it from email fragments.

At minimum, the package should state:

- which nets or net classes require impedance control

- target values and whether they are single-ended or differential

- the intended stackup or approved material options

- nominal finished thickness and copper assumptions

- whether coupon testing or specific impedance reporting is expected

- what dimensions are fixed versus adjustable during stackup review

If the design still has open questions, it is better to send a direct contact request before freezing the release package. That conversation is often faster than correcting an ambiguous quote after the fact.

Common Controlled Impedance PCB Design Mistakes That Cause Quote Rework

Most controlled-impedance release problems are not caused by advanced field-solver errors. They come from mismatches between design assumptions and fabrication communication.

One common mistake is routing the board first and asking whether the stackup can support it later. Another is calling out impedance targets without naming which layers and structures they apply to. Teams also lose time when they use a calculator value as if it were production approval, even though the supplier may need different copper or dielectric assumptions to build the board reliably.

A few other recurring issues are worth checking before release:

- trace widths that are theoretically valid but too tight for comfortable process margin

- differential pair spacing that conflicts with assembly breakout or via escape needs

- stackup notes that do not match the actual routed layer usage

- missing clarification on whether equivalent material substitutions are acceptable

- impedance requirements discussed in meetings but absent from the controlled release package

When those gaps exist, the release turns into a clarification exercise instead of a clean manufacturing handoff.

How to Prepare a Cleaner Handoff for Fabrication and Assembly

The last step in an impedance-controlled release is making sure the package communicates intent as clearly as the layout itself. A clean handoff should give the manufacturer enough structure to review stackup feasibility, quote risk, and production assumptions without guessing.

A practical release package usually includes fabrication data, drill files, stackup notes, impedance callouts, board thickness targets, assembly context where relevant, and a clear revision marker. It also helps to say whether the board is an exploratory prototype, a validation build, or a production-intent release, because that changes how much flexibility the supplier has when proposing adjustments.

If the goal is a smooth quote and fewer late surprises, the release should end with explicit communication: what must stay fixed, what can be tuned during review, and what performance assumptions matter most. That is the difference between a board that is merely routed and one that is truly ready for manufacturing.

FAQ About Controlled Impedance PCB Design

Is controlled impedance PCB design only for RF boards?

No. RF boards often need it, but many high-speed digital designs also depend on controlled impedance when reflections, timing margin, crosstalk, or channel loss become sensitive enough that ordinary routing assumptions are no longer safe.

Can a calculator alone approve controlled impedance PCB design?

No. A calculator is useful for early direction, but production-ready impedance control work still depends on the supplier's stackup, material options, copper model, and process capability.

Should impedance requirements be reviewed before asking for a quote?

Yes. Early review helps prevent quote churn, because the supplier can flag stackup conflicts, unrealistic geometry, or missing material assumptions before the board package is frozen.

Conclusion

Strong controlled-impedance planning aligns simulation intent, stackup planning, routing geometry, and supplier communication before fabrication begins. In practice, good controlled impedance PCB design gives quoting teams and fabricators a much clearer starting point. When those pieces are reviewed together, signal-sensitive boards are easier to quote, easier to build, and far less likely to need avoidable rework after release.