Leitfaden für Multilayer-PCB-Design: Stackup-Planung, Lagenzahl und Fertigungs-Trade-offs

SUNTOP Electronics

Beim Multilayer-PCB-Design geht es nicht einfach nur darum, zusätzliche Kupferlagen hinzuzufügen, sobald eine Leiterplatte zu voll wirkt. In realen Projekten bedeutet Multilayer-PCB-Design, noch vor der Freigabe zur Fertigung Routing-Dichte, Signal Integrity, Stromverteilung, mechanische Randbedingungen, Bestückbarkeit und Kosten sauber gegeneinander abzuwägen.

Eine einfache zweilagige Leiterplatte reicht für viele Produkte aus. Wenn ein Design jedoch dichteres Routing, sauberere Rückstrompfade, controlled impedance, engere Bauteil-Breakouts oder ein robusteres EMI-Verhalten verlangt, wird ein Multilayer-Aufbau oft zur realistischeren Lösung. Die entscheidende Frage ist nicht, ob mehr Lagen „fortschrittlicher“ wirken. Entscheidend ist, ob diese Lagen tatsächlich ein elektrisches oder fertigungstechnisches Problem lösen.

Genau deshalb sollte gutes Multilayer-PCB-Design früh beginnen. Teams, die mit der Lagenentscheidung bis zum Ende des Layouts warten, erzeugen häufig vermeidbare Schleifen: Power-Planes werden kompromittiert, die Stackup-Absicht bleibt unklar, und der Hersteller muss vor dem Angebot erst grundlegende Annahmen nachfragen. Sinnvoller ist es, zunächst festzulegen, was die Leiterplatte leisten muss, und daraus die Lagenstruktur abzuleiten.

Dieser Leitfaden zeigt, wann eine Multilayer-Strategie echten Mehrwert schafft, wie Sie über Stackup und Referenzebenen nachdenken sollten, welche Herstellbarkeits-Trade-offs bei Vias und Escape Routing auftreten und was Sie vorbereiten sollten, bevor ein Lieferant das Design prüft.

Was Multilayer-PCB-Design bedeutet und wann zusätzliche Lagen sinnvoll sind

Mit Multilayer-PCB ist in der Regel eine Leiterplatte mit drei oder mehr leitfähigen, miteinander laminierten Lagen gemeint. In der Praxis starten viele Projekte aber konkret mit 4-, 6- oder 8-Lagen-Entscheidungen. Der Hauptgrund für einen Multilayer-Aufbau ist nicht Optik, sondern genügend Platz für Signale, Planes und Bauteil-Breakouts zu schaffen, ohne das Layout mit fragwürdigen Kompromissen zu belasten.

Zusätzliche Lagen sind in der Praxis oft sinnvoll, wenn eine Leiterplatte Folgendes braucht:

- dedizierte Referenzebenen für saubere Rückstrompfade

- eine klarere Trennung zwischen störenden und empfindlichen Signalen

- controlled-impedance-Planung für High-Speed- oder RF-Netze

- stabilere Stromverteilung über mehrere Versorgungsschienen

- dichteres BGA- oder Fine-Pitch-Escape-Routing

- weniger Engstellen rund um Stecker, Speicher, Prozessoren oder Mixed-Signal-Bereiche

Multilayer-PCB-Design kann auch die Flächeneffizienz verbessern. Statt den Umriss zu vergrößern, damit das Routing auf weniger Lagen irgendwie passt, lässt sich ein Teil der Komplexität in das Stackup verlagern und die Leiterplatte dadurch kompakter halten. Das kann dem Gehäuseeinbau und dem Kabelmanagement helfen, erhöht aber zugleich den Fertigungsaufwand. Dieser Trade-off sollte also bewusst getroffen werden.

Der Kernpunkt ist: Multilayer-PCB-Design sollte von elektrischen und fertigungstechnischen Anforderungen getrieben sein, nicht von der vagen Annahme, dass mehr Lagen automatisch besser sind. Wenn ein Design ohne Einbußen bei Leistung und Zuverlässigkeit mit weniger Lagen sauber lösbar ist, kann das die bessere geschäftliche Entscheidung sein.

So planen Sie Stackup, Signallagen und Referenzebenen

Das Herzstück eines Multilayer-Designs ist die Stackup-Planung. Sobald die Lagenzahl feststeht, sollte der nächste Schritt nicht sofortiges Routen sein, sondern die Frage, welche Aufgabe jede Lage übernimmt und wie benachbarte Lagen diese Aufgabe unterstützen. Ein gutes Multilayer-PCB-Design sorgt dafür, dass jede wichtige Signallage eine klare Referenzebene hat, statt Planes erst nachträglich als Restfläche zu behandeln.

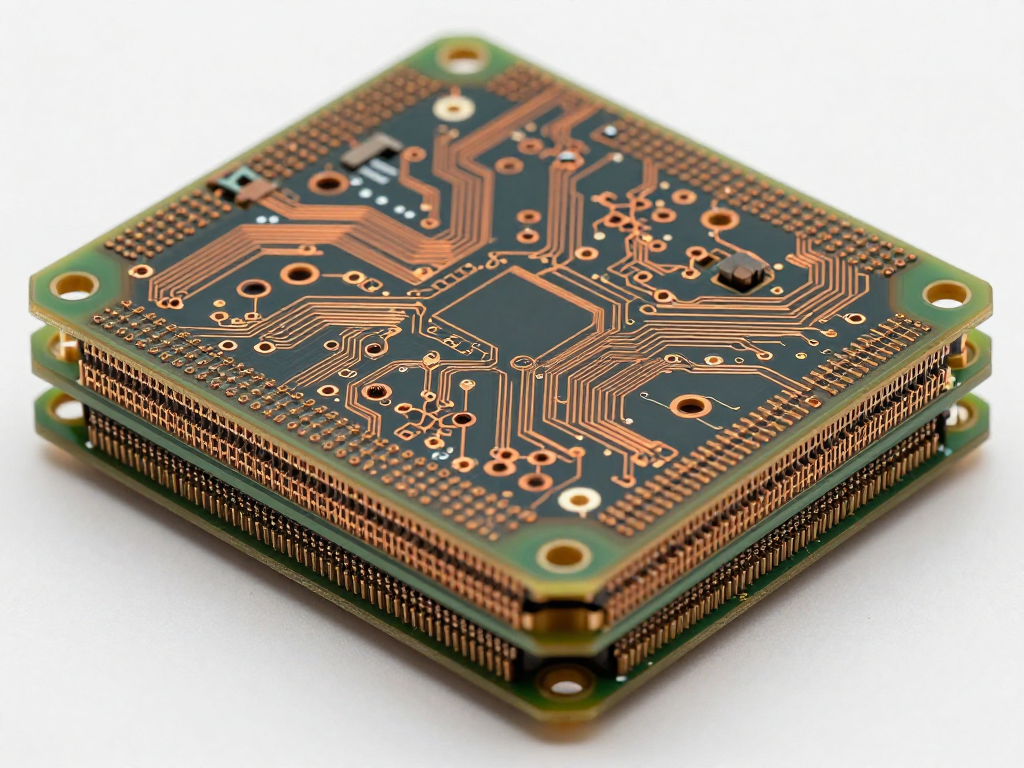

Board-Detail mit gerouteten Leiterbahnen, Via-Bohrungen und typischen Merkmalen dichter Multilayer-PCB-Fertigung.

Ein sinnvoller Einstieg ist, die Rollen der Lagen grob in einige praktische Gruppen zu unterteilen:

- Signallagen für kritisches Routing

- Ground-Referenzebenen zur Führung des Rückstroms

- Power-Lagen oder größere Kupferbereiche

- sekundäre Routing-Lagen für weniger kritische Signale oder Breakout-Arbeit

Wird diese Planung übersprungen, entstehen oft fragmentierte Planes, unnötige Lagenwechsel oder Routing-Strukturen, die im CAD vollständig aussehen, sich in der Hardware aber schlecht verhalten. Das ist besonders riskant bei schnellen Flanken, längeren Bussen, impedanzkritischen Netzen oder gemischten Analog-/Digital-Bereichen.

Für frühe Machbarkeitsprüfungen kann der PCB Stackup Planner helfen, grobe Dicke, Kupferverteilung und angenommene Lagenrollen vorab zu vergleichen. Wenn das Verhalten einer Übertragungsleitung relevant ist, ist der Online-Impedanzrechner ein nützliches Vorab-Tool. Er sollte jedoch die Diskussion mit dem Lieferanten unterstützen und nicht die tatsächliche Fertigungsabstimmung ersetzen.

Die Qualität der Referenzebene ist wichtig, weil das Routing-Verhalten eng mit Rückstrompfaden und Feldstruktur verknüpft ist. Im weiteren Kontext von Signal Integrity heißt das: kritische Leiterbahnen möglichst nah an einer stabilen Referenz führen und Plane-Splits unter diesen Netzen vermeiden. Wenn das Design controlled routing auf Außenlagen nutzt, können typische Microstrip-Strukturen Teil der Stackup-Diskussion sein. Die endgültige Geometrie muss aber immer zum gewählten Material und zum tatsächlichen Fertigungsprozess passen.

Gutes Multilayer-PCB-Design heißt außerdem, die Stackup-Absicht klar zu dokumentieren. Der Hersteller sollte nicht raten müssen, ob eine Lage als durchgehende Referenzebene gedacht ist, ob in einem Bereich Kupferbalance wichtig ist oder ob impedanzkontrolliertes Routing optional oder verpflichtend ist.

Via-Strategie, Escape Routing und Trade-offs bei der Fertigbarkeit

Die Wahl der Via-Struktur kann über Erfolg oder Probleme im Multilayer-PCB-Design entscheiden. Eine Leiterplatte sieht oft nur deshalb routbar aus, weil das Layout-Tool viele Lagenwechsel zulässt. Jeder Wechsel bringt jedoch zusätzliche Kosten, Fertigungsgrenzen und mögliche Nebenwirkungen für Signalverhalten oder Montage mit sich. Ein gutes Stackup behandelt Vias daher als kontrollierte Ressource und nicht als unbegrenzte Bequemlichkeit.

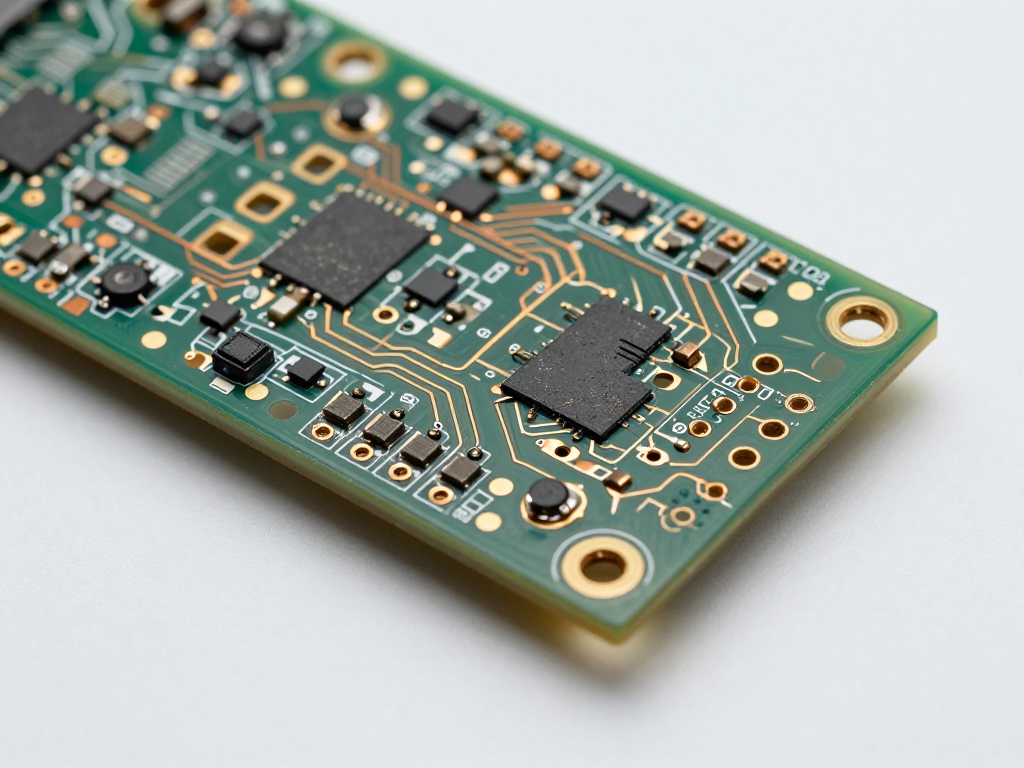

Board-Detail mit dichtem Routing, Bauteilplatzierung und metallisierten Bohrungen in einem Multilayer-PCB-Layout.

Through-Vias sind oft die einfachste und wirtschaftlichste Lösung, verbrauchen aber Routing-Kanäle über den gesamten Stack. Blind Vias, Buried Vias oder Microvias können die Dichte erhöhen, insbesondere rund um Fine-Pitch-Bauteile, steigern aber auch Prozesskomplexität und Prüfaufwand. Bevor Sie sie einsetzen, sollte klar sein, warum Standard-Vias nicht mehr ausreichen.

Escape Routing ist ein weiterer Punkt, an dem Multilayer-PCB-Design zu einer echten Abwägung wird. Dichte BGAs, Speicherinterfaces und Steckerfelder treiben Designs oft zu mehr Lagen. Die richtige Antwort ist jedoch nicht immer, sofort zusätzliche Lagen zu ergänzen. Manchmal reduzieren Pin-Swaps, geänderte Bauteilorientierung, eine bessere Fanout-Planung oder ein saubererer Floorplan den Druck bereits, bevor das Stackup erweitert werden muss.

Aus Sicht der Fertigbarkeit sollten diese Punkte früh geprüft werden:

- ob die Via-Struktur zum tatsächlichen Routing-Bedarf passt

- ob Annahmen zu Anti-Pad und Plane-Clearance realistisch sind

- ob Hochstrompfade durch zu enge Übergänge gezwungen werden

- ob Lagenwechsel unnötige Unterbrechungen im Rückstrompfad erzeugen

- ob dichte Breakout-Bereiche noch genügend Fertigungsspielraum lassen

Je komplexer die Via-Strategie wird, desto wichtiger ist das Gespräch mit dem Hersteller, bevor die Leiterplatte als angebotsreif gilt.

Häufige Multilayer-PCB-Fehler, die Kosten oder Verzögerungen verursachen

Die meisten Probleme im Multilayer-PCB-Design entstehen nicht durch einen einzigen spektakulären Fehler. Meist sind es mehrere kleine Entscheidungen, die in der Fertigungsprüfung ungünstig zusammenwirken.

Ein typischer Fehler ist, die Lagenzahl zu spät festzulegen. Wenn die Leiterplatte bereits überfüllt ist und Timing- oder Stromversorgungsprobleme auftauchen, wird die Stackup-Entscheidung oft hastig getroffen, ohne genügend Zeit, Routing und Planes sinnvoll neu zu ordnen.

Ein weiterer Fehler ist, von „einer 6-Lagen-Platine“ zu sprechen, ohne das Stackup tatsächlich definiert zu haben. Die reine Lagenzahl sagt dem Lieferanten nicht, welche Lage welche Aufgabe hat, welche Netze impedanzkritisch sind oder wo Plane-Kontinuität zwingend ist.

Ein dritter Fehler besteht darin, den Einfluss mechanischer und bestückungsrelevanter Randbedingungen zu unterschätzen. Connector-Keepouts, Versteifungen, Gehäusedruckpunkte, Bauteilhöhen und Testzugänglichkeit beeinflussen unmittelbar, wie praktikabel ein bestimmter Stackup- oder Routing-Ansatz wirklich ist.

Teams verlieren außerdem Zeit, wenn sie erfolgreiche CAD-DRCs mit echter Fertigbarkeitsprüfung verwechseln. DRCs zeigen nur, dass Regelwerte eingehalten werden. Sie garantieren nicht, dass das Freigabepaket die Designabsicht für Fertigung und Bestückung klar genug kommuniziert.

Schließlich werden manche Leiterplatten unnötig überentwickelt. Multilayer-PCB-Design sollte reale Randbedingungen lösen, nicht schwache Vorarbeit hinter einem teureren Stackup verstecken. Wenn die Lagenzahl nur deshalb gestiegen ist, weil Platzierung, Partitionierung oder Power-Strategie nie sauber bereinigt wurden, wird das Angebot diese Ineffizienz meist schnell offenlegen.

So bereiten Sie ein besseres Multilayer-Paket für die Fertigungsprüfung vor

Selbst ein sauber geplantes Stackup und durchdachtes Routing bringen wenig, wenn das Freigabepaket die Designabsicht nicht leicht verständlich vermittelt. Bevor Sie ein Angebot oder Engineering-Feedback anfordern, sollte der Lieferant sowohl die Geometrie der Leiterplatte als auch die Überlegungen dahinter nachvollziehen können.

Ein gutes Review-Paket enthält in der Regel:

- Fertigungsdaten und Bohrdateien passend zur aktuellen Revision

- Stackup-Notizen mit den vorgesehenen Lagenrollen und kritischen Randbedingungen

- Impedanzziele, wo sie relevant sind

- klare Angaben zu Board-Outline, Slots, Ausschnitten und mechanischen Hinweisen

- Bestückungsdaten, falls parallel auch eine PCBA-Prüfung stattfinden soll

- kurze Hinweise dazu, was fest vorgegeben und was noch verhandelbar ist

Hilfreich ist auch, die Prioritäten offen zu benennen. Ist das Stackup wegen EMC-Anforderungen bereits festgelegt, oder ist das Team offen für Herstellervorschläge? Sind bestimmte Lagen für controlled routing reserviert, oder darf der Fertiger eine praktischere Struktur vorschlagen? Solche Informationen beeinflussen sowohl die Qualität der Prüfung als auch die Geschwindigkeit des Angebots.

Wenn das Team vor der finalen Freigabe Feedback vom Lieferanten einholen möchte, ist es oft am sinnvollsten, das Design frühzeitig über die Kontaktseite zu teilen und kurz Board-Ziel, aktuellen Lagenplan und bekannte Risikobereiche zu erläutern. Das ist deutlich produktiver, als kommentarlos Daten zu schicken und einzelne Rückfragen abzuwarten.

FAQ zum Multilayer-PCB-Design

Wann sollte ein Team von 2 Lagen auf ein Multilayer-PCB wechseln?

In der Regel dann, wenn sich Routing-Engstellen, Referenzebenenqualität, Stromverteilung, EMI-Kontrolle oder Impedanzanforderungen auf 2 Lagen nicht mehr sauber lösen lassen. Der Schritt zum Multilayer-Aufbau sollte aus klaren elektrischen und fertigungstechnischen Gründen erfolgen, nicht nur, weil das Board „komplex wirkt“.

Verbessert ein Multilayer-Aufbau die Signal Integrity automatisch?

Nein. Ein Multilayer-Design schafft bessere Voraussetzungen für Rückstrompfade und Impedanzkontrolle, aber nur dann, wenn Stackup und Routing diese Möglichkeiten auch korrekt nutzen. Eine schlechte Plane-Strategie auf vielen Lagen kann immer noch schlechter abschneiden als eine disziplinierte, einfachere Leiterplatte.

Ist eine höhere Lagenzahl insgesamt immer teurer?

Die Fertigungskosten für das Bare Board steigen in der Regel mit einem komplexeren Stackup. Die Gesamtkosten eines Projekts hängen aber von mehr ab als nur vom Leiterplattenpreis. Wenn ein Multilayer-Design Fläche spart, Redesigns vermeidet, Yield verbessert oder die Bestückung vereinfacht, kann sich die Gesamtkostenlage trotzdem verbessern.

Welche Informationen sollten vor einer Angebotsanfrage für eine Multilayer-Leiterplatte mit dem Hersteller geteilt werden?

Mindestens aktuelle Fertigungsdaten, Bohrinformationen, die Stackup-Absicht, mechanische Hinweise und alle relevanten Randbedingungen zu Impedanz, Material oder Bestückung. Je klarer dieses Paket ist, desto leichter kann der Hersteller einschätzen, ob das Multilayer-PCB-Design bereits angebotsreif ist oder noch Anpassungen braucht.

Fazit

Gutes Multilayer-PCB-Design ist eine Planungsdisziplin und nicht bloß eine Entscheidung über die Lagenzahl. Wenn Teams früh die Rollen im Stackup definieren, Referenzebenen schützen, Vias gezielt einsetzen und die Fertigungsabsicht klar kommunizieren, sinkt die Reibung im Angebotsprozess und vermeidbare Redesign-Schleifen werden seltener.

Die besten Ergebnisse entstehen meist dann, wenn die Leiterplatte als gemeinsamer Engineering-Review zwischen Layout, elektrischen Zielen, mechanischen Randbedingungen und Fertigungsrealität verstanden wird. Passiert diese Abstimmung vor der Freigabe, verläuft der Weg in Fertigung und Bestückung in der Regel deutlich sauberer.